# ARM® Architecture Reference Manual Supplement Statistical Profiling Extension, for ARMv8-A

# Architecture Reference Manual Supplement Statistical Profiling Extension

Copyright © 2017 ARM Limited or its affiliates. All rights Reserved.

#### Release information

The following changes have been made to this document.

| Date          | Issue | Confidentiality  | Change      |

|---------------|-------|------------------|-------------|

| 29 March 2017 | A     | Non-Confidential | First Issue |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version shall prevail.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement specifically covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

Words and logos marked with ® or TM are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at <a href="http://www.arm.com/about/trademarks/guidelines/index.php">http://www.arm.com/about/trademarks/guidelines/index.php</a>.

Copyright © 2017 ARM Limited or its affiliates. All rights reserved. ARM Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

**LES-PRE-20327**

In this document, where the term ARM is used to refer to the company it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### **Web Address**

http://www.arm.com

# Contents

| Pre | eface | •••••    |                                                                               | 7  |

|-----|-------|----------|-------------------------------------------------------------------------------|----|

|     | Refe  | rences   |                                                                               | 7  |

|     |       |          |                                                                               |    |

|     |       |          |                                                                               |    |

| 1   | Intr  | oduction | l                                                                             | 8  |

|     | 1.1   |          | cal profiling                                                                 |    |

|     | 1.1   | Statisti | car proming                                                                   |    |

| 2   | ΔRN   | Av8 2 St | atistical Profiling Extension                                                 | q  |

| _   | 2.1   |          | vasive behavior                                                               |    |

|     | 2.1   | 2.1.1    | Disabled in AArch32                                                           |    |

|     | 2.2   |          | ng the sample population                                                      |    |

|     | 2.2   | 2.2.1    | Operation sampling                                                            |    |

|     |       | 2.2.2    | Random number generation.                                                     |    |

|     |       | 2.2.3    | Defining where operations are sampled                                         |    |

|     |       | 2.2.4    | Sample collisions                                                             |    |

|     |       | 2.2.5    | Operations that might be excluded from the sample population                  |    |

|     | 2.3   |          | ted data                                                                      |    |

|     | 2.5   | 2.3.1    | Additional information for each profiled branch or exception return           |    |

|     |       | 2.3.2    | Additional information for each profiled memory access operation              |    |

|     |       | 2.3.3    | Additional information for each profiled conditional instruction (including c |    |

|     |       |          | branches)                                                                     |    |

|     |       | 2.3.4    | Additional information for other operations                                   |    |

|     |       | 2.3.5    | Sample Records that might be incomplete                                       |    |

|     | 2.4   | Enablii  | ng sampling and filtering sample records                                      |    |

|     | 2.5   |          | ing records of sampled operations                                             |    |

|     | 2.6   |          | Extensions                                                                    |    |

|     | 2.7   |          | tion with the Embedded Cross Trigger                                          |    |

|     | 2.8   |          | nreaded implementations                                                       |    |

|     |       |          |                                                                               |    |

| 3   | Prog  | grammei  | rs' Model Overview                                                            | 20 |

|     | 3.1   | Contro   | lling when an operation is sampled                                            |    |

|     |       | 3.1.1    |                                                                               |    |

|     |       | 3.1.2    | Behavior of the sample interval counter while profiling is enabled            | 21 |

|     |       | 3.1.3    | Behavior of the sample interval counter while profiling is disabled           | 22 |

|     |       | 3.1.4    | Sample collision behavior                                                     |    |

|     | 3.2   | Enable   | and Filtering controls                                                        |    |

|     |       | 3.2.1    | Enabling Profiling                                                            |    |

|     |       | 3.2.2    | Filtering sample records                                                      | 23 |

|     |       | 3.2.3    | Pseudocode details of filtering and enable controls                           |    |

|     | 3.3   |          | lling the data that is collected                                              |    |

|     |       | 3.3.1    | Pseudocode details of collection controls                                     |    |

|     | 3.4   |          | ofiling Buffer                                                                |    |

|     |       | 3.4.1    | Restrictions on the current write pointer                                     |    |

|     |       | 3.4.2    | The owning Exception level                                                    |    |

|     |       | 3.4.3    | Memory access types and coherency                                             |    |

|     |       | 3.4.4    | TLB operations                                                                | 31 |

#### Architecture Reference Manual Supplement Statistical Profiling Extension, for ARMv8-A

|   |      | 3.4.5      | Effect on the exclusive monitors                         |    |

|---|------|------------|----------------------------------------------------------|----|

|   |      | 3.4.6      | Pseudocode details of the Profiling Buffer               |    |

|   | 3.5  |            | Buffer management event                                  |    |

|   |      | 3.5.1      | Prioritization of Profiling Buffer management events     |    |

|   |      | 3.5.2      | Buffer full event                                        |    |

|   |      | 3.5.3      | Faults and watchpoints                                   |    |

|   |      | 3.5.4      | External aborts                                          |    |

|   | 3.6  | Synchron   | nization and Statistical Profiling                       |    |

|   |      | 3.6.1      | UNPREDICTABLE behavior                                   | 38 |

| 4 | Deta | iled Progi | rammers Model                                            | 39 |

|   | 4.1  | Register   | index                                                    | 39 |

|   | 4.2  |            | resets                                                   |    |

|   | 4.3  |            | descriptions                                             |    |

|   |      | 4.3.1      | PMBIDR EL1, Profiling Buffer ID Register                 |    |

|   |      | 4.3.2      | PMBLIMITR EL1, Profiling Buffer Limit Address Register   |    |

|   |      | 4.3.3      | PMBPTR EL1, Profiling Buffer Write Pointer Register      |    |

|   |      | 4.3.4      | PMBSR EL1, Profiling Buffer Status/syndrome Register     |    |

|   |      | 4.3.5      | PMSCR EL1, Statistical Profiling Control Register (EL1)  |    |

|   |      | 4.3.6      | PMSCR_EL12, Statistical Profiling Control Register (EL1) |    |

|   |      | 4.3.7      | PMSCR EL2, Statistical Profiling Control Register (EL2)  |    |

|   |      | 4.3.8      | PMSEVFR EL1, Sampling Event Filter Register              |    |

|   |      | 4.3.9      | PMSFCR EL1, Sampling Filter Control Register             |    |

|   |      | 4.3.10     | PMSICR EL1, Sampling Interval Counter Register           |    |

|   |      | 4.3.11     | PMSIDR EL1, Sampling Profiling ID Register               |    |

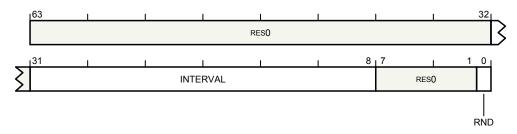

|   |      | 4.3.12     | PMSIRR EL1, Sampling Interval Reload Register            |    |

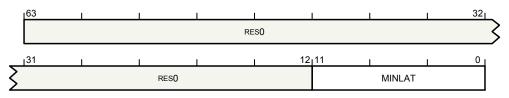

|   |      | 4.3.13     | PMSLATFR EL1, Sampling Latency Filter Register           |    |

|   |      |            |                                                          |    |

| 5 |      |            | .t                                                       |    |

|   | 5.1  |            | W                                                        |    |

|   |      | 5.1.1      | Packets                                                  |    |

|   |      | 5.1.2      | Records                                                  |    |

|   |      | 5.1.3      | Byte order                                               |    |

|   |      | 5.1.4      | Protocol framing packets and forwards compatibility      |    |

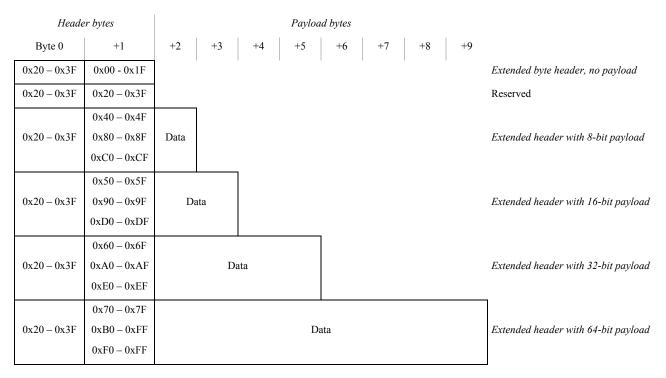

|   | 5.2  |            | el encodings                                             |    |

|   |      | 5.2.1      | 8-bit headers                                            |    |

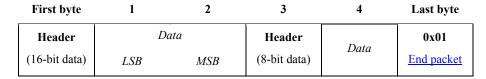

|   |      | 5.2.2      | 16-bit headers                                           |    |

|   | 5.3  | Packets.   |                                                          |    |

|   |      | 5.3.1      | Address packet                                           |    |

|   |      | 5.3.2      | Alignment command                                        |    |

|   |      | 5.3.3      | Context packet                                           |    |

|   |      | 5.3.4      | Counter packet                                           |    |

|   |      | 5.3.5      | Data Source packet                                       |    |

|   |      | 5.3.6      | End packet                                               |    |

|   |      | 5.3.7      | Events packet                                            |    |

|   |      | 5.3.8      | Operation Type packet                                    |    |

|   |      | 5.3.9      | Padding                                                  |    |

|   |      | 5.3.10     | Timestamp packet                                         | 94 |

|   | 5.4  | IMPLEME    | ENTATION DEFINED packets                                 | 96 |

# **Preface**

This document describes the Statistical Profiling Extension, an optional extension for implementations of the ARMv8-A architecture profile ARMv8.1 or later, and must be read in conjunction with the *ARM*® *Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.*

#### References

This document refers to the following documents and links.

| Reference | Document number | Author | Document name                                                               |

|-----------|-----------------|--------|-----------------------------------------------------------------------------|

| [1]       | ARM DDI 0487    | ARM    | ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile |

| [2]       | ARM-DEN-0029    | ARM    | ARM® Server Base System Architecture                                        |

#### **Feedback**

ARM welcomes feedback on its documentation.

If you have comments on the content of this manual, send an e-mail to errata@arm.com. Give:

- The title.

- The document and version number, ARM DDI 0586A.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### 1 Introduction

This section introduces the Statistical Profiling Extension, a mechanism for profiling software and hardware using randomized sampling.

The Statistical Profiling Extension is an optional extension to the ARMv8 architecture, and is introduced as part of ARMv8.2. An implementation that includes the Statistical Profiling Extension must be compliant with at least the ARMv8.1 architecture profile.

The Statistical Profiling Extension introduces a new barrier instruction, the Profiling Synchronization Barrier (PSB CSYNC), which is described in detail in the *ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile*.

The Statistical Profiling Extension introduces a set of registers that are specific to the Statistical Profiling Extension architecture. These registers are accessed as System registers and are described in detail in this supplement.

In addition, the Statistical Profiling Extension adds a limited number of fields to the following ARMv8-A System registers in AArch64 state:

- ID AA64DFR0 EL1.PMSVer

- MDCR EL2.{TPMS, E2PB}

- MDCR EL3.NSPB

For details about these changes, see the ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

# 1.1 Statistical profiling

Statistical profiling is a four stage process.

- 1. An operation is chosen from a sample population, at a programmable interval that might have some random, or pseudorandom, perturbation.

- 2. A trace of the sampled operation is taken. This includes the PC, events, timings, and data addresses, related to the sampled operation. This is the profiling operation.

- 3. Before a sample record is created, it is possible to filter out potential sample records generated by the profiling operation by reference to, any or all of the following:

- a. The type of operation.

- b. The Exception level.

- c. Event and latency.

- 4. A sample record is created that contains the traced information. Sample records that meet the criteria of the filter are written to and stored in a memory buffer. These sample records can be processed by software when the memory buffer is full.

# 2 ARMv8.2 Statistical Profiling Extension

This section gives an overview of the Statistical Profiling Extension. Sections 3 and 4 describe the programmers' model in detail:

- Programmers' Model Overview.

- Detailed Programmers Model.

#### 2.1 Non-invasive behavior

Statistical Profiling is a non-invasive debug operation:

- While profiling is enabled, the operation and performance of the processing element (PE) must not be significantly impacted between sampled operations, that is, other than for writing out sample records and processing Profiling Buffer management events.

- The performance of the sampled operation and the performance of the PE in general must not be significantly impacted. The sample records are not written to memory until after the sampled operation has completed. However, this does not apply when the user selects a collection of physical addresses for data access operations. In this case, the impact is IMPLEMENTATION DEFINED.

- The profiling operation to write sample records must not be excessively impactful on the performance of the sampled operation or the performance of the PE generally.

#### 2.1.1 Disabled in AArch32

Statistical profiling is disabled in AArch32 state.

# 2.2 Defining the sample population

All samples are taken from a *population* of *operations*. The population is *dynamic* rather than *static*. That is, if a program executes the same operation multiple times (for example, because of loops and subroutines) then that operation appears multiple times in the population.

The operations are an IMPLEMENTATION DEFINED choice between:

- Architecture instructions.

- IMPLEMENTATION DEFINED microarchitectural operations ( $\mu$ -ops).

Architecture instruction means a single instruction that is defined by the ARMv8 instruction set architecture in AArch64 state.

An architecture instruction might create one or more  $\mu$ -ops at any point in the execution pipeline. The definition of a  $\mu$ -op is implementation specific. An architecture instruction might create more than one  $\mu$ -op for each instruction. A  $\mu$ -op might also be removed or merged with another  $\mu$ -op in the execution stream, so an architecture instruction might create no  $\mu$ -ops for an instruction.

Any arbitrary translation of architecture instructions to an equivalent sequence of  $\mu$ -ops is permitted. In some implementations, the relationship between architecture instructions and  $\mu$ -ops might vary over time.

| Note                                         |                                                               |

|----------------------------------------------|---------------------------------------------------------------|

| Sampling from architecture instructions does | not require that the instruction is architecturally executed. |

|                                              |                                                               |

#### 2.2.1 Operation sampling

A sample operation is as follows:

- 1. A sampling interval is written to a sample interval counter by software. The interval is measured in operations.

- 2. The sample interval counter is decremented by hardware for each operation when sampling is enabled

- 3. When the sample interval counter reaches zero, then:

- a) If random perturbation is enabled, the PE continues to count for a random number of further operations while sampling is enabled.

- An operation is chosen for profiling.

Note

The choice of operation around the sampling point is arbitrary. The chosen operation might be the operation for which the sample interval counter reached 0, or the next operation. The choice must be applied consistently so as not to introduce sampling bias.

- 4. The sample interval counter is reloaded and the process loops to step 2. It is IMPLEMENTATION DEFINED whether the sample interval counter is reloaded before step 3.a) or at step 3.b). That is, before or after counting the random number of further operations. See Controlling when an operation is sampled.

- 5. The chosen operation is marked as the sampled operation. The PE collects information about the sampled operation as it executes by a profiling operation.

- 6. When the sampled operation is completed, the sample record is captured.

The lifespan of a sampled operation completes when any of the following is true:

- The instruction or μ-op is committed to the architectural state of the PE (including completion by generating a synchronous exception).

- The speculative instruction or  $\mu$ -op is discarded because of misspeculation.

- The instruction or  $\mu$ -op is replayed, on some microarchitectures.

For more information on misspeculation and replaying instructions or  $\mu$ -ops see Operations that might be excluded from the sample population.

#### 2.2.2 Random number generation

The random number generator is IMPLEMENTATION DEFINED. Implementations might use a pseudorandom number. The random number generator must be reset into a useable state. An implementation might include IMPLEMENTATION DEFINED registers to further configure the random number generator.

#### 2.2.3 Defining where operations are sampled

The exact point in the sampled lifetime of operations at which sampled operations are chosen for profiling is IMPLEMENTATION DEFINED.

ARM recommends that the point at which operations are sampled is linked to the definition of the Performance Monitoring Extension (PMU) STALL\_FRONTEND and STALL\_BACKEND events, so that sampling records information for STALL BACKEND stalls.

#### 2.2.4 Sample collisions

The maximum number of sampled operations that a PE can support simultaneously in flight is IMPLEMENTATION DEFINED. If the maximum number of sampled operations is in flight at the point when a new sample operation must be taken, the new sample is said to have *collided* with a previous sampled operation.

The PE records the fact that a sampled operation has collided with another sampled operation. Software can also count the number of collisions and gauge the impact of the collisions.

See Sample collision behavior.

#### 2.2.5 Operations that might be excluded from the sample population

It is IMPLEMENTATION DEFINED whether each of the following operations is part of the sample population:

- Operations on misspeculated paths.

- Operations (specifically  $\mu$ -ops) that do not relate to any architecture instruction.

- Operations that generate non-architectural exceptions.

If the operation is not part of the sample population, the operation does not cause the sample interval counter to decrement, is not counted by the <u>SAMPLE\_POP</u> event and therefore is never sampled.

If the operation is part of the sample population, the operation causes the sample interval counter to decrement, is counted by the <u>SAMPLE\_POP</u> event, and might be sampled and counted by the <u>SAMPLE\_FEED</u> event.

See also Sample Records that might be incomplete.

#### 2.3 Collected data

Unless otherwise stated all sample records that are generated by a profiling operation contain:

- A timestamp, if enabled. This is one of:

- CNTPCT EL0.

- CNTVCT EL0.

It is IMPLEMENTATION DEFINED how this timestamp relates to the sampled operation. It might be the time when the sampled operation was taken or any later time during the lifetime of the sampled operation, that is, up to the time when the sampled operation is completed.

If the Generic Timer system counter is disabled and timestamps are enabled, then it is IMPLEMENTATION DEFINED whether:

- The Statistical Profiling Extension behaves as if timestamps are disabled.

- The timestamp that is collected in the sample record is UNKNOWN.

This behavior describes when CNTEN.EN is cleared to 0. This behavior does not apply when the Generic Timer system counter is enabled but not accessible at the current Exception level.

- The context, if enabled, which is one or more of:

- CONTEXTIDR EL1.

- CONTEXTIDR EL2.

- The Exception level.

- The Security state.

- Information about whether the sampled operation generated an exception:

- The target address for an exception generating operation is not collected.

- Information about whether the sampled operation completed execution.

If the sampled operation completes execution and does not generate an exception, the sample record also contains:

- The PC virtual address for the sampled operation.

- Information about whether the sampled operation is a branch, a load, a store, or other.

- Information about whether the sampled operation is conditional, conditional select, or not.

- The total latency, a cycle count of the lifetime of the sampled operation.

- The issue latency, a cycle count from the start of the lifetime of the sampled operation up to the point when the sampled operation starts executing. A sampled operation might be delayed, for example because the input operands were not available.

The architecture defines a set of additional data that is collected in the sample record for each sampled operation. This is described in the following subsections, and comprises:

- Events.

- Cycle counters. Cycle count values as described in this architecture, which for a particular implementation are fixed with an IMPLEMENTATION DEFINED value, might be omitted from the sample record.

- Addresses.

In addition, the architecture permits IMPLEMENTATION DEFINED events, counters, and addresses to be collected.

#### 2.3.1 Additional information for each profiled branch or exception return

For a completed branch or exception return sampled operation, the profiling operation must record:

- The sampled operation type as an unconditional branch or a conditional branch. Sampled exception returns are treated as unconditional branches by the Statistical Profiling Extension.

- The target virtual address of the branch. The target virtual address includes the Exception level and Security state of the target.

#### Architecture Reference Manual Supplement Statistical Profiling Extension, for ARMv8-A

| Note                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If the sampled operation is an illegal exception return, it is IMPLEMENTATION DEFINED whether the context information recorded in the target virtual address is the actual target context, or the target context that is described by the SPSR. |

| If the PE implements branch prediction, whether the branch was correctly predicted or mispredicted.                                                                                                                                             |

| Whether the branch was taken or not taken.                                                                                                                                                                                                      |

| Whether the branch was direct or indirect.                                                                                                                                                                                                      |

| See also | <u>Additional</u> | information f | or each | profiled | conditional | instruction ( | including | conditional | branches) |

|----------|-------------------|---------------|---------|----------|-------------|---------------|-----------|-------------|-----------|

|          |                   |               |         |          |             |               |           |             |           |

| —— Note ·   |                         | <del></del>         |                    |     |

|-------------|-------------------------|---------------------|--------------------|-----|

| A sampled o | peration that generates | an exception is not | treated as a branc | :h. |

#### 2.3.2 Additional information for each profiled memory access operation

For a completed load, store, or atomic sampled operation that does not generate an exception, the profiling operation must record:

- The data virtual and, if enabled, physical addresses being accessed.

- If the applicable Top Byte Ignore (TBI) bit is set to one, the virtual address includes any topbyte tag.

- The physical address is the address the PE accesses in the physical address space, and so includes the Secure Address Space Identifier.

- The sampled operation type, which includes:

- Whether the sampled operation is a load, store, or atomic.

- Whether the sampled operation is Load-Exclusive, Store-Exclusive or Load-acquire, Store-release.

- Whether the sampled operation accesses the general-purpose or SIMD&FP registers.

- The translation latency, a cycle count from the virtual address being generated to the physical address being returned by the MMU.

- Whether the sampled operation accessed the Level 1 data cache and resulted in a hit.

- Whether the sampled operation accessed the data TLB and resulted in a hit.

- An optional, IMPLEMENTATION DEFINED, record of whether the sampled operation accessed Last Level data cache and resulted in a hit.

- An optional, IMPLEMENTATION DEFINED, record of whether the sampled operation accessed *another socket* in a multi-socket system.

- An optional, IMPLEMENTATION DEFINED, indicator of the data source for a load.

For each of the Last level cache and another socket indicators, it is IMPLEMENTATION DEFINED whether this information is present only for load accesses, only for store accesses, for neither, or for both.

| A store might be marked as not accessing a cache or another socket because it completed before doing so. For example, the write was held in a write buffer. This behavior is IMPLEMENTATION DEFINED, and software must be cautious when interpreting such events. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If architecture instructions are sampled, then, for a sampled load/store operation that is not single-copy atomic, the data addresses are the lowest address that is accessed by the sampled operation.                                                           |

| Otherwise the information is for the $\mu$ -op that is sampled.                                                                                                                                                                                                   |

| —— Example ———                                                                                                                                                                                                                                                    |

| If an architectural load instruction is split into an address generation $\mu$ -op and a load $\mu$ -op, then when generating the sample record and filtering based on operation type:                                                                            |

| • If the address generation $\mu$ -op is sampled, the sampled operation is treated as <i>other</i> .                                                                                                                                                              |

| • If the load $\mu$ -op is sampled, the sampled operation is treated as a load.                                                                                                                                                                                   |

| For more information see <u>Filtering sample records</u> and <u>Operation Type packet</u> .                                                                                                                                                                       |

| 2.3.3 Additional information for each profiled conditional instruction (including conditional branches)                                                                                                                                                           |

| For a completed conditional branch, conditional select, conditional move, or conditional increment sampled operation, the profiling operation must record:                                                                                                        |

| That the sampled operation was conditional.                                                                                                                                                                                                                       |

| <ul> <li>Whether the condition passed or failed.</li> </ul>                                                                                                                                                                                                       |

| If a conditional instruction fails its condition code test, it is IMPLEMENTATION DEFINED whether any of the information for the sampled operation that is generated by executing the sampled operation is recorded. Any                                           |

#### 2.3.4 Additional information for other operations

packet, the value in the packet is UNKNOWN.

For cache maintenance operations by virtual address, cache prefetch, or address translation instructions, the profiling operation:

A conditional branch operation fails its condition code test. It is IMPLEMENTATION DEFINED whether the sample record contains a branch target Address packet. If the sample record contains a branch target Address

value that is recorded and is the result of executing the sampled operation is UNKNOWN.

- Captures an IMPLEMENTATION DEFINED subset of the information captured for a load instruction.

- Treats the operation type as *other* when generating the sample record and filtering based on operation type.

See Filtering sample records and Operation Type packet.

— Example —

Note —

## 2.3.5 Sample Records that might be incomplete

It is IMPLEMENTATION DEFINED whether the sample record for a misspeculated operation or an operation generating a non-architectural exception, if sampled, is written to the Profiling Buffer:

- If a sample record of a misspeculated operation or an operation generating a non-architectural exception is written to the Profiling Buffer, then neither event #0 (generated exception) nor event #1 (architecturally retired) are set in the record Events packet.

- If a sample record of a misspeculated operation or an operation generating a non-architectural exception is not captured into the Profiling Buffer, then no event packets are output and the sample is not counted by the <a href="Manual England">SAMPLE\_FILTRATE</a> event.

| Note                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| It is IMPLEMENTATION DEFINED whether such operations can be sampled. See <u>Operations that might be excluded from the sample population</u> .        |

| All sample records written to the Profiling Buffer contain the <u>Events packet</u> and either the <u>End packet</u> or the <u>Timestamp packet</u> . |

| If the sampled operation generates an exception, it is UNPREDICTABLE whether the sample record contains any other information.                        |

| Where a sampled operation generates an exception and the type of exception means that a particular item is                                            |

not computed by the sampled operation, that information is not collected by the profiling operation. See

# ——Example ———

Synchronization and Statistical Profiling.

A sampled operation generates a Translation Fault. The physical address for the sampled operation was not generated by the MMU and cannot be recorded.

# 2.4 Enabling sampling and filtering sample records

Profiling can be disabled at individual Exception levels, and is always disabled at EL3.

When profiling is disabled, no sample records are collected and the sample interval counters retain their values and do not decrement.

Collected sample records can also be filtered by type, by event, and by latency:

- By type, a combination of any or all of:

- Branches.

- Loads.

- Stores.

- By event, a combination of any or all of:

- Mispredicted branches.

- TLB missing accesses.

- Level 1 cache refilling accesses.

- Architecturally retired instructions.

- By latency:

- Whether the total latency of the operation exceeds a programmable threshold.

When filtering is enabled, sample records that do not meet the filtering criteria are discarded and are not written to the Profiling Buffer.

## 2.5 Capturing records of sampled operations

Sample records are written by hardware in a packetized format to a buffer in memory:

- The start and end pointers for this buffer are specified in System registers.

- The pointers are virtual address pointers.

- The PE generates a <u>Profiling Buffer management event</u> when the Profiling Buffer is full.

For more information see **The Profiling Buffer**.

#### 2.6 PMU Extensions

Two sets of additional events are defined for the PMU. If the Statistical Profiling and Performance Monitoring Extensions are implemented, then the events that are listed in <u>Table 1</u> must be implemented.

Table 1: Statistical Profiling PMU events

| Event number | Event mnemonic | Description                                                                                                                                                                                                                                        |  |

|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x4000       | SAMPLE_POP     | Sample Population                                                                                                                                                                                                                                  |  |

|              |                | The counter increments for each operation that might be sampled, whether or not the operation was sampled. Operations that are executed at an Exception level or Security state in which profiling is disabled are not counted.                    |  |

| 0x4001       | SAMPLE_FEED    | Sample taken                                                                                                                                                                                                                                       |  |

|              |                | The counter increments each time the sample interval counter reaches zero and is reloaded, and the sample does not collide with a previous sample. Samples that are removed by filtering, or discarded, and not written to the buffer are counted. |  |

|              |                | The number of operations that might be sampled is counted by <u>SAMPLE_POP</u> , meaning these two events can determine the sampling ratio.                                                                                                        |  |

| 0x4002 | SAMPLE_FILTRATE  | Sample taken and not removed by filtering                                                                                                                                                                                                                                                     |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                  | The counter increments each time that a completed sample record is checked against the filters and not removed. Sample records that are not removed by filtering, but are discarded before being written to the Profiling Buffer because of a Profiling Buffer management event, are counted. |

|        |                  | The number of operations that are sampled is counted by <a href="Mailto:SAMPLE_FEED">SAMPLE_FEED</a> meaning that:                                                                                                                                                                            |

|        |                  | • If all filtering is disabled, then <u>SAMPLE_FILTRATE</u> counts the same as <u>SAMPLE_FEED</u> .                                                                                                                                                                                           |

|        |                  | • These two events can determine the proportion of sampled operations that met the filtering criteria.                                                                                                                                                                                        |

| 0x4003 | SAMPLE_COLLISION | Sample collided with a previous sample                                                                                                                                                                                                                                                        |

|        |                  | The counter increments for each sample record that is taken when<br>the previous sampled operation has not completed generating its<br>sample record.                                                                                                                                         |

--- Note ----

These events are discoverable through a read of PMCEID0\_EL0[35:32].

The Statistical Profiling Extension also introduces the events that are listed in <u>Table 2</u>. These events can be included in any implementation of the PMU Extension, even if the Statistical Profiling Extension is not implemented.

Table 2: Additional PMU events

| Event number | Event mnemonic | Description                                                                                                                                                        |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0031       | REMOTE_ACCESS  | Access to another socket in a multi-socket system                                                                                                                  |

|              |                | The counter counts each memory read operation or memory write operation that causes an access to another socket in a multi-socket system.                          |

|              |                | It is IMPLEMENTATION DEFINED whether an access that causes a snoop into another socket but does not return data from or pass data to the remote socket is counted. |

| 0x0032       | LL CACHE       | Last Level cache access                                                                                                                                            |

|              | _              | The counter counts each memory read operation or memory write operation that causes a cache access to at least the Last Level data or unified cache.               |

|              |                | Cache maintenance instructions do not count as events.                                                                                                             |

| 0x0033 | LL_CACHE_MISS    | Last Level cache miss                                                                                                                                                                                                                                                                                                |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                  | The counter counts each memory-read operation or memory write operation that causes a cache access to at least the Last Level data or unified cache, but is not completed by the Last Level cache. That is, either of the following:                                                                                 |

|        |                  | <ul> <li>A memory read operation that does not return data from the<br/>Last Level cache.</li> </ul>                                                                                                                                                                                                                 |

|        |                  | • A memory write operation that does not update the Last Level cache.                                                                                                                                                                                                                                                |

|        |                  | The counter does not count operations that are completed by a cache above the Last Level cache.                                                                                                                                                                                                                      |

|        |                  | The number of Last Level cache accesses is counted by <a href="LL_CACHE"><u>LL_CACHE</u></a> , meaning that these two events can determine the Last Level cache miss ratio.                                                                                                                                          |

| 0x0034 | DTLB_WALK        | Access to data TLB that causes a translation table walk                                                                                                                                                                                                                                                              |

|        |                  | The counter counts each memory read or memory write operation that causes a refill of a data or unified TLB involving at least one translation table walk access. This includes each complete or partial translation table walk that causes an access to memory, including to data or translation table walk caches. |

|        |                  | The number of TLB accesses is counted by the L1D_TLB event, meaning that these two events can determine the data TLB miss ratio.                                                                                                                                                                                     |

| 0x0035 | ITLB_WALK        | Access to instruction TLB that causes a translation table walk                                                                                                                                                                                                                                                       |

|        |                  | The counter counts each instruction memory access that causes a refill of an instruction TLB, involving at least one translation table walk access. This includes each complete or partial translation table walk that causes an access to memory, including to data or translation table walk caches.               |

|        |                  | The number of TLB accesses is counted by the L1I_TLB event, meaning that these two events can determine the instruction TLB miss ratio.                                                                                                                                                                              |

| 0x0036 | LL_CACHE_RD      | Last level cache access, read As LL_CACHE, but counts only memory read operations.                                                                                                                                                                                                                                   |

| 0x0037 | LL_CACHE_MISS_RD | Last level cache miss, read                                                                                                                                                                                                                                                                                          |

|        |                  | As <u>LL_CACHE_MISS_RD</u> , but counts only memory read operations.                                                                                                                                                                                                                                                 |

|        |                  | The number of Last Level cache accesses is counted by <a href="LL_CACHE_RD"><u>LL_CACHE_RD</u></a> , meaning that these two events can determine the Last Level cache read miss ratio.                                                                                                                               |

| 0x0038                  | REMOTE_ACCESS_RD                                                    | Access to another socket in a multi-socket system, read                                                                                                                                                                            |

|-------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                     | As <u>REMOTE_ACCESS</u> , but counts only memory read operations. It is possible to calculate the number of memory write operations by deducting the number of REMOTE_ACCESS_RD events from REMOTE_ACCESS events.                  |

| Not                     | to                                                                  |                                                                                                                                                                                                                                    |

|                         |                                                                     | read of PMCEID1 EL0[24:17] and PMCEID1[24:17].                                                                                                                                                                                     |

| These eve               | ints are discoverable tillough a                                    | read of FMCEID1_EL0[24.17] and FMCEID1[24.17].                                                                                                                                                                                     |

|                         |                                                                     | -                                                                                                                                                                                                                                  |

| 2.7 Ir                  | nteraction with the E                                               | mbedded Cross Trigger                                                                                                                                                                                                              |

|                         |                                                                     | n out, CTI input trigger 2 is asserted. This trigger might also be ATION DEFINED debug features.                                                                                                                                   |

| 2.8 N                   | lultithreaded implen                                                | nentations                                                                                                                                                                                                                         |

| In a multit             | threaded implementation, Stat                                       | istical Profiling is implemented per-thread.                                                                                                                                                                                       |

| The samp                | le interval counter counts only                                     | operations for the thread that is being profiled.                                                                                                                                                                                  |

| Latency an an operation | •                                                                   | each cycle for the PE for which the thread was active and could issue                                                                                                                                                              |

|                         | tecture does not define feature tween threads.                      | s for inter-thread profiling and does not support sharing the Profiling                                                                                                                                                            |

| Not                     | te                                                                  | -                                                                                                                                                                                                                                  |

| processors              | s that are implemented using a<br>s at the lowest affinity level is | i-threaded when the lowest level of affinity consists of logical a multi-threading type approach. That is, the performance of very interdependent. On such an implementation, the value of mest implemented Exception level, is 1. |

# 3 Programmers' Model Overview

Profiling is controlled by System registers. There is no direct EL0 access to the control registers and by default profiling is disabled. The programmers' model is divided into the following parts:

- Sampling controls:

- Controlling when an operation is sampled.

- Enable and Filtering controls.

- Controlling the data that is collected.

- Profiling Buffer controls:

- The Profiling Buffer.

- Profiling Buffer management.

- Synchronization and Statistical Profiling.

# 3.1 Controlling when an operation is sampled

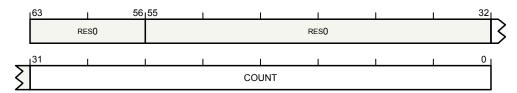

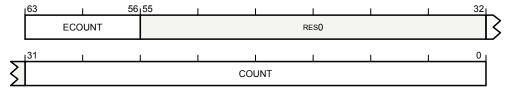

The sample interval counter, <u>PMSICR\_EL1.COUNT</u> controls when an operation is selected for sampling. In some implementations, a secondary sample interval counter, <u>PMSICR\_EL1.ECOUNT</u>, is also used.

The following sections describe the operation of the sample interval counters.

Details of the random or pseudorandom number generator used when <u>PMSIRR\_EL1.RND</u> is set to 1 are IMPLEMENTATION DEFINED. See Random number generation.

#### 3.1.1 Initializing one or more sample interval counters

When the PE moves from a state where profiling is disabled to a state where profiling is enabled:

- If <u>PMSICR EL1</u> is nonzero, then sampling restarts from the current values in <u>PMSICR EL1</u>.

- If <u>PMSICR\_EL1</u> is zero, then it is loaded with an initial value. The behavior depends on <u>PMSIRR\_EL1.RND</u> and an IMPLEMENTATION DEFINED choice discoverable by a read of <u>PMSIDR\_EL1.ERnd</u>.

#### If PMSIRR EL1.RND is cleared to 0:

- PMSICR\_EL1.COUNT[31:8] is set to PMSIRR\_EL1.INTERVAL.

- PMSICR EL1. COUNT [7:0] is set to  $0 \times 00$ .

#### If **PMSIRR EL1.RND** is set to 1 and **PMSIDR EL1.ERnd** is 0:

- PMSICR EL1.COUNT[31:8] is set to PMSIRR EL1.INTERVAL.

- PMSICR\_EL1.COUNT[7:0] is set to a random or pseudorandom value in the range 0x00 to 0xFF.

#### If **PMSIRR EL1.RND** is set to 1 and **PMSIDR EL1.ERnd** is 1:

- PMSICR EL1.COUNT[31:8] is set to PMSIRR EL1.INTERVAL.

- PMSICR EL1.COUNT[7:0] is set to 0x00.

#### 3.1.2 Behavior of the sample interval counter while profiling is enabled

While profiling is enabled, the counters control when an operation is selected for sampling. The behavior depends on <a href="MSIRR\_EL1.RND">PMSIRR\_EL1.RND</a> and an IMPLEMENTATION DEFINED choice discoverable in <a href="PMSIDR\_EL1.ERnd">PMSIDR\_EL1.ERnd</a>.

#### If PMSIRR EL1.RND is cleared to 0:

While nonzero, the sample interval counter decrements by 1 for each member of the sample population. When the counter reaches zero:

- A member of the sampling population is selected for sampling.

- The counter is set as follows:

- PMSICR EL1.COUNT[31:8] is set to PMSIRR EL1.INTERVAL.

- PMSICR EL1.COUNT[7:0] is set to 0x00.

| Note                                                    |                                     |

|---------------------------------------------------------|-------------------------------------|

| Because the counter counts down to zero, when PMSI      | IRR_EL1.RND is cleared to 0 the     |

| interval between operations being selected for sampling | ng is $(INTERVAL \times 256 + 1)$ . |

#### If PMSIRR EL1.RND is set to 1 and PMSIDR EL1.ERnd is 0:

While nonzero, the sample interval counter decrements by 1 for each member of the sample population. When the counter reaches zero:

- A member of the sampling population is selected for sampling.

- The counter is set as follows:

- PMSICR EL1.COUNT[31:8] is set to PMSIRR EL1.INTERVAL.

- PMSICR\_EL1.COUNT[7:0] is set to a random or pseudorandom value in the range 0x00 to 0xff.

| Note |  |  |  |  |

|------|--|--|--|--|

|------|--|--|--|--|

When <u>PMSIRR\_EL1.RND</u> is set to 0 and <u>PMSIDR\_EL1.ERnd</u> is 1, the mean interval between operations being selected for sampling is ( $INTERVAL \times 256 + 128$ ), if the random number generator is uniform.

#### If **PMSIRR EL1.RND** is set to 1 and **PMSIDR EL1.ERnd** is 1:

While nonzero, the primary sample interval counter decrements by 1 for each member of the sample population. When the primary counter reaches zero:

- The primary sample interval counter is reloaded.

- A secondary sample interval counter, <u>PMSICR\_EL1.ECOUNT</u>, is set to a random or pseudorandom value in the range 0x00 to 0xFF.

While the secondary sample interval counter is nonzero, the secondary sample interval counter decrements by 1 for each member of the sample population. The primary sample interval counter also continues to decrement because it is also nonzero.

When the secondary sample interval counter reaches zero, an operation is selected for sampling.

|                   | Architecture Reference Manual Supplement Statistical Profiling Extension, for ARMv8-A                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | —— Note ———                                                                                                                                                                                                                                                                                                                            |

|                   | When <u>PMSIRR_EL1.RND</u> is set to 1 and <u>PMSIDR_EL1.ERnd</u> is 1, the mean interval between operations being selected for sampling is ( $INTERVAL \times 256 + 1$ ), if the random number generator is uniform.                                                                                                                  |

|                   | vior of the sample interval counter while profiling is disabled                                                                                                                                                                                                                                                                        |

| When profiling    |                                                                                                                                                                                                                                                                                                                                        |

| Î                 | rations are selected for sampling.                                                                                                                                                                                                                                                                                                     |

|                   | aple records are collected.                                                                                                                                                                                                                                                                                                            |

| • The sar         | mple interval counters retain their values and do not decrement.                                                                                                                                                                                                                                                                       |

|                   | le collision behavior                                                                                                                                                                                                                                                                                                                  |

| On a sample co    |                                                                                                                                                                                                                                                                                                                                        |

|                   | MU event <u>SAMPLE_COLLISION</u> is generated.                                                                                                                                                                                                                                                                                         |

|                   | R_EL1.COLL is set to 1.                                                                                                                                                                                                                                                                                                                |

| visible to instru | ntext synchronization event an indirect write to <a href="MBSR_EL1.COLL">PMBSR_EL1.COLL</a> is guaranteed to be ctions in program order after the sampled operation that collided. There is no guarantee of ut a context synchronization event. For more information see <a href="Synchronization">Synchronization and Statistical</a> |

| Note              | <del></del>                                                                                                                                                                                                                                                                                                                            |

| This means that   | t following a context synchronization event <a href="PMBSR_EL1.COLL">PMBSR_EL1.COLL</a> will not change on entry to a filing is disabled.                                                                                                                                                                                              |

| 3.2 Enab          | le and Filtering controls                                                                                                                                                                                                                                                                                                              |

| 3.2.1 Enabl       | ing Profiling                                                                                                                                                                                                                                                                                                                          |

| Profiling is disa | bled if the Profiling Buffer is disabled, including when:                                                                                                                                                                                                                                                                              |

| • PMBLI           | MITR_EL1.E is cleared to 0 or PMBSR_EL1.S is set to 1.                                                                                                                                                                                                                                                                                 |

| • Executi         | ing at a higher Exception level than the Profiling Buffer owning Exception level.                                                                                                                                                                                                                                                      |

|                   | ing in the Security state that is not the Security state of the owning Exception level. is in Debug state.                                                                                                                                                                                                                             |

|                   |                                                                                                                                                                                                                                                                                                                                        |

<u>The owning Exception level</u> is controlled by MDCR\_EL3.NSPB and MDCR\_EL2.E2PB.

In a guest operating system or Secure state, PMSCR EL1.E1SPE enables profiling at EL1 and PMSCR\_EL1.E0SPE at EL0.

<u>PMSCR\_EL1</u>. <u>{E1SPE</u>, <u>E0SPE</u>} and <u>PMSCR\_EL2</u>. <u>{E2SPE</u>, <u>E0HSPE</u>} enable sampling by Exception level:

Note -

• In a hypervisor or host operating system, <a href="MSCR\_EL2.E2SPE">PMSCR\_EL2.E0HSPE</a> at EL0.

Table 3 summarizes the controls for enabling by Exception level and Security state.

Table 3: Enabling by Exception level and Security state (for all Exception levels using AArch64)

| Controls                                                    |          |         |             |      |                                                                     | Sampling enabled at                                                   |       |       |        |

|-------------------------------------------------------------|----------|---------|-------------|------|---------------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|--------|

| <u>S</u>                                                    | <u>E</u> | NS      | <b>NSPB</b> | E2PB | TGE                                                                 | EL3                                                                   | EL2   | EL1   | EL0    |

| 1                                                           | X        | X       | X           | X    | X                                                                   | D                                                                     | D     | D     | D      |

| 0                                                           | 0        | X       | X           | X    | X                                                                   | D                                                                     | D     | D     | D      |

|                                                             | 1        | 1       | 0b1X        | 0b1X | 0                                                                   | D                                                                     | D     | E1SPE | E0SPE  |

|                                                             |          |         |             |      | 1                                                                   | D                                                                     | D     | n/a   | D      |

|                                                             |          |         |             | 0b00 | 0                                                                   | D                                                                     | E2SPE | E1SPE | E0SPE  |

|                                                             |          |         |             |      | 1                                                                   | D                                                                     | E2SPE | n/a   | E0HSPE |

|                                                             |          |         | 0b0X        | X    | X                                                                   | D                                                                     | D     | D     | D      |

|                                                             |          | 0       | 0b1X        | X    | X                                                                   | D                                                                     | n/a   | D     | D      |

|                                                             |          |         | 0b0X        | X    | X                                                                   | D                                                                     | n/a   | E1SPE | E0SPE  |

| <u>S</u> = ]                                                | PMBSI    | R_EL1.S |             |      |                                                                     | D = Disabled.                                                         |       |       |        |

| <u>E</u> = ]                                                | PMBLI    | MITR_E  | <u>L1.E</u> |      |                                                                     | E2SPE = Enabled if <u>PMSCR_EL2.E2SPE</u> == 1, disabled otherwise.   |       |       |        |

| $NS = SCR\_EL3.NS$                                          |          |         |             |      |                                                                     | E1SPE = Enabled if <u>PMSCR_EL1.E1SPE</u> == 1, disabled otherwise.   |       |       |        |

| $\underline{NSPB} = \underline{MDCR\_EL3.NSPB}$             |          |         |             |      |                                                                     | E0HSPE = Enabled if <u>PMSCR_EL2.E0HSPE</u> == 1, disabled otherwise. |       |       |        |

| $\underline{E2PB} = \underline{MDCR\_EL2}.\underline{E2PB}$ |          |         |             |      | E0SPE = Enabled if <u>PMSCR_EL1.E0SPE</u> == 1, disabled otherwise. |                                                                       |       |       |        |

| TGE                                                         | E = HCI  | R_EL2.T | GE          |      |                                                                     |                                                                       |       |       |        |

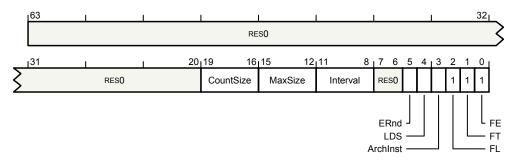

#### 3.2.2 Filtering sample records

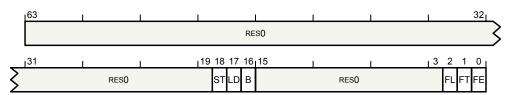

<u>PMSFCR\_EL1.FT</u> enables filtering by operation type. When enabled <u>PMSFCR\_EL1</u>.{<u>ST, LD, B</u>} define the collected types:

- ST enables collection of store sampled operations, including all atomic operations.

- <u>LD</u> enables collection of load sampled operations, including atomic operations that return a value to a register.

- <u>B</u> enables collection of branch sampled operations, including direct and indirect branches and exception returns.

| Note                                                                              |

|-----------------------------------------------------------------------------------|

| When $\mu$ -op sampling is implemented, filtering is based on the $\mu$ -op type. |

| <del></del>                                                                       |

|                                                                                   |

|                                                                                   |

<u>Table 4</u> summarizes the controls for filtering by operation type.

Table 4: Filtering by Operation type

| PMSFCR_EL1. |           |           |          | Operation type |       |        |       |

|-------------|-----------|-----------|----------|----------------|-------|--------|-------|

| <u>FT</u>   | <u>LD</u> | <u>ST</u> | <u>B</u> | Load           | Store | Branch | Other |

| 0           | X         | X         | X        | С              | С     | С      | С     |

| 1           | 0         | 0         | 0        | D              | D     | D      | D     |

|             |           |           | 1        | D              | D     | С      | D     |

|             |           | 1         | 0        | D              | С     | D      | D     |

|             |           |           | 1        | D              | С     | С      | D     |

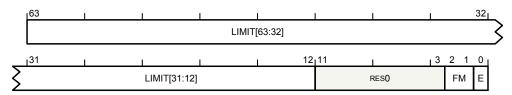

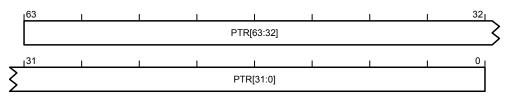

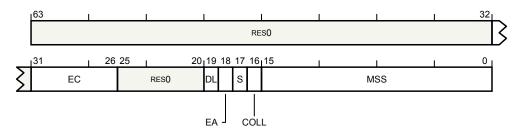

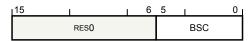

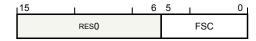

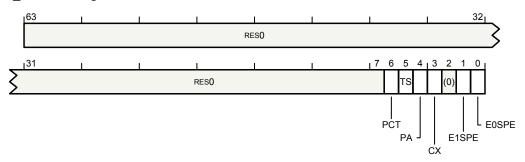

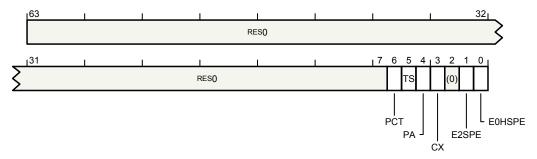

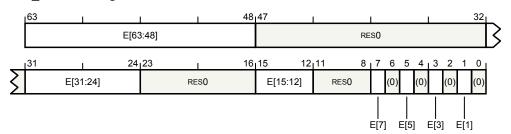

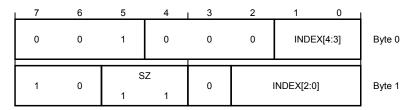

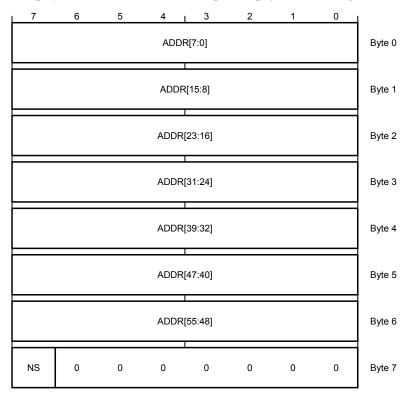

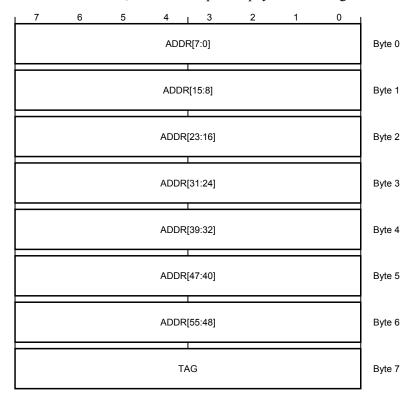

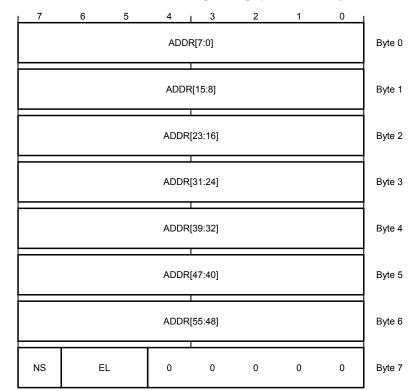

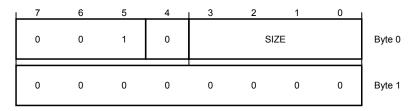

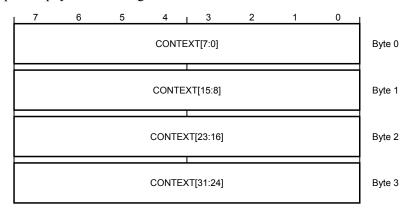

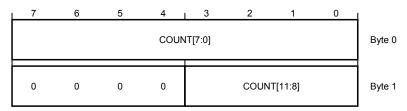

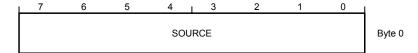

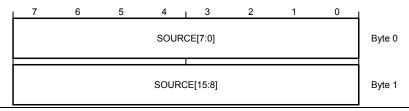

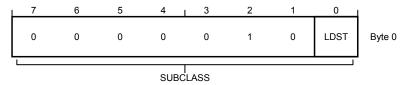

|             | 1         | 0         | 0        | С              | D     | D      | D     |