# **Fixed Virtual Platforms**

Version 1.4

VE Cortex-A15 Cortex-A7 CCI-400 User Guide

### **Fixed Virtual Platforms**

### VE Cortex-A15 Cortex-A7 CCI-400 User Guide

Copyright © 2014-2016 ARM. All rights reserved.

### Release Information

### **Document History**

| Issue | Date             | Confidentiality  | Change                                                     |

|-------|------------------|------------------|------------------------------------------------------------|

| A     | 30 November 2014 | Non-Confidential | New document for Fast Models v9.1, from DUI0585C for v9.0. |

| В     | 28 February 2015 | Non-Confidential | Update for v9.2.                                           |

| С     | 31 May 2015      | Non-Confidential | Update for v9.3.                                           |

| D     | 31 August 2015   | Non-Confidential | Update for v9.4.                                           |

| Е     | 30 November 2015 | Non-Confidential | Update for v9.5.                                           |

| F     | 29 February 2016 | Non-Confidential | Update for v9.6.                                           |

| G     | 31 May 2016      | Non-Confidential | Update for v10.0.                                          |

### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at <a href="http://www.arm.com/about/trademark-usage-guidelines.php">http://www.arm.com/about/trademark-usage-guidelines.php</a>

Copyright © 2014-2016, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

### Web Address

http://www.arm.com

# Contents

# Fixed Virtual Platforms VE Cortex-A15 Cortex-A7 CCI-400 User Guide

|           | Pret  | ace                                                                      |            |

|-----------|-------|--------------------------------------------------------------------------|------------|

|           |       | About this book                                                          | 7          |

| Chapter 1 | Intro | oduction                                                                 |            |

|           | 1.1   | About system models                                                      | 1-10       |

|           | 1.2   | About the VE FVP                                                         | 1-11       |

|           | 1.3   | About the Cortex-A15 Cortex-A7 CCI-400 FVP                               | 1-12       |

| Chapter 2 | Gett  | ing Started with the Cortex-A15 Cortex-A7 CCI-400 FVP                    |            |

|           | 2.1   | Supported operating systems for the Cortex-A15 Cortex-A7 CCI-400 FVP     | 2-14       |

|           | 2.2   | Licenses for Cortex-A15 Cortex-A7 CCI-400                                | 2-15       |

|           | 2.3   | Installing the Cortex-A15 Cortex-A7 CCI-400                              | 2-16       |

|           | 2.4   | Running models from the command line                                     | 2-17       |

|           | 2.5   | Running models using Model Debugger                                      | 2-19       |

|           | 2.6   | Configuring the model                                                    | 2-20       |

| Chapter 3 | Prog  | grammers Reference                                                       |            |

|           | 3.1   | Fixed Virtual Platforms for VE platform functionality                    | 3-23       |

|           | 3.2   | Fixed Virtual Platform VE Cortex-A15 Cortex-A7 CCI-400 memory map and in | terrupts . |

|           |       |                                                                          | 3-24       |

|           | 3.3   | CS2 peripheral memory map                                                | 3-25       |

|           | 3.4   | CS3 peripheral memory map                                                | 3-26       |

|           |       |                                                                          |            |

| 3.5  | Model parameters                                                         | 3-27 |

|------|--------------------------------------------------------------------------|------|

| 3.6  | Motherboard peripheral parameters                                        | 3-28 |

| 3.7  | Motherboard virtual component parameters                                 | 3-31 |

| 3.8  | CoreTile parameters                                                      | 3-33 |

| 3.9  | Memory map differences between the VE hardware and the system model      | 3-37 |

| 3.10 | Memory aliasing differences between the VE hardware and the system model | 3-38 |

| 3.11 | Features not present in the model                                        | 3-39 |

| 3.12 | Features partially implemented in the model                              | 3-40 |

| 3.13 | Restrictions on the processor models                                     | 3-41 |

| 3.14 | Timing considerations                                                    | 3-42 |

| 3.15 | Bus consistency messages                                                 | 3-43 |

| 3.16 | Multiple entries in the cache with the same security world               | 3-44 |

| 3.17 | Mismatched attributes                                                    | 3-45 |

| 3.18 | Cache Coherent Interconnect snoop and DVM enables                        | 3-47 |

| 3.19 | Snoop or DVM messages received while in reset                            | 3-48 |

| 3.20 | Invalidation of dirty lines                                              | 3-49 |

| 3.21 | Dual Cluster System Configuration Block                                  | 3-50 |

| 3.22 | Reset architecture                                                       | 3-67 |

| 3.23 | Interrupt Generation Trickbox                                            | 3-68 |

# Preface This preface introduces the Fixed Virtual Platforms VE Cortex-A15 Cortex-A7 CCI-400 User Guide. It contains the following: • About this book on page 7.

### About this book

This book describes how to configure and use the *Fixed Virtual Platform* (FVP) VE Cortex-A15 Cortex-A7 CCI-400 Cache Coherent Interconnect. The model enables software applications to run on a virtual implementation based on the *Versatile™ Express* (VE) memory map. The model contains a CoreTile that models an ARM Cortex-A15 SMP and an ARM Cortex-A7 SMP connected using the CCI-400.

### Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

Read this for an introduction to the *Versatile Express* (VE) Cortex-A15 Cortex-A7 CCI-400 *Fixed Virtual Platform* (FVP).

### Chapter 2 Getting Started with the Cortex-A15 Cortex-A7 CCI-400 FVP

This chapter describes how to use the model. It also contains information regarding license key requirements and installation.

### Chapter 3 Programmers Reference

Read this for a description of the functionality that the model supports, including the memory map and configuration parameters.

### Glossary

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM Glossary for more information.

### Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

### monospace bold

Denotes language keywords when used outside example code.

### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *ARM glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

### **Feedback**

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Fixed Virtual Platforms VE Cortex-A15 Cortex-A7 CCI-400 User Guide.

- The number ARM DUI0848G.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| ARN | I al | SO | wel | comes | general | suggestions | for | additions | and | improv | ements. |

|-----|------|----|-----|-------|---------|-------------|-----|-----------|-----|--------|---------|

|-----|------|----|-----|-------|---------|-------------|-----|-----------|-----|--------|---------|

| That were were general suggestions for warmons and improvements.                                    |

|-----------------------------------------------------------------------------------------------------|

| Note                                                                                                |

| ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the |

| represented document when used with any other PDF reader.                                           |

### Other information

- ARM Information Center.

- ARM Technical Support Knowledge Articles.

- Support and Maintenance.

- ARM Glossary.

# Chapter 1 **Introduction**

Read this for an introduction to the *Versatile Express* (VE) Cortex-A15 Cortex-A7 CCI-400 *Fixed Virtual Platform* (FVP).

Describes system models, the VE FVPs, and the VE Cortex-A15 Cortex-A7 CCI-400 FVP.

It contains the following sections:

- 1.1 About system models on page 1-10.

- 1.2 About the VE FVP on page 1-11.

- 1.3 About the Cortex-A15 Cortex-A7 CCI-400 FVP on page 1-12.

### 1.1 About system models

The Fixed Virtual Platforms (FVPs) enable you to develop software without the requirement for actual hardware.

The software models provide a *Programmer's View* (PV) model of processors and peripheral devices. The functional behavior of a model is based on functionality in equivalent real hardware. Absolute timing accuracy is sacrificed to achieve fast simulated execution speed. To confirm software functionality, use the PV models. However, do not rely on them for:

- The accuracy of cycle counts.

- Low-level component interactions.

- Other hardware-specific behavior.

### 1.2 About the VE FVP

Versatile Express (VE) is a hardware development platform that ARM produces.

You can split a VE system into the following sub-components:

### Motherboard

The Motherboard Express  $\mu$ ATX includes a range of peripherals that provide a general purpose I/O platform. The motherboard contains two daughterboard sockets for CoreTile Express or LogicTile Express boards. For more information, see the *Motherboard Express*  $\mu$ ATX V2M-P1 Technical Reference Manual.

### **Daughterboard**

Field Programmable Gate Array (FPGA) and processor daughterboards provide:

- · Custom peripherals.

- Early access to processor designs.

- Production test chips.

System memory is also implemented on the daughterboard.

### **Processor**

An implementation of an ARM processor.

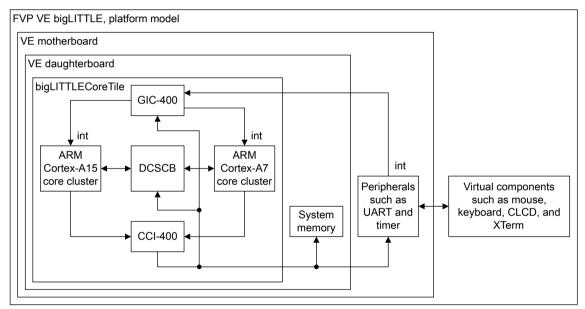

The VE Fixed Virtual Platform (FVP) is a system model implemented in software. The model contains:

- Virtual implementations of a motherboard.

- A single daughterboard.

- A specific ARM processor.

- Associated interconnections.

The model is based on the VE platform memory map, but it is not intended to be an accurate representation of a specific VE hardware revision. The VE FVP supports selected peripherals as this document describes. The supplied model is sufficiently complete and accurate to boot the same operating system images as for the VE hardware. The model is developed using the ARM® Fast Models library product.

### 1.3 About the Cortex-A15 Cortex-A7 CCI-400 FVP

The Dual Cluster System (DCS) contains the Cortex-A15 and Cortex-A7 clusters.

This includes the interconnect required to implement the heterogeneous multi-processing platform, and to support the software-controlled powering up and powering down of the Cortex-A15 and Cortex-A7 clusters, and task migration between the two. The interconnect is implemented using:

### **CCI-400 Cache Coherent Interconnect**

Provides bus interconnect and coherency functions in a single module. It supports connectivity for up to two ACE masters. For example, a Cortex-A15 processor and a Cortex-A7 processor. For more information, see the *CCI-400 Cache Coherent Interconnect Architecture Specification*.

### **Dual Cluster System Configuration Block (DCSCB)**

Provides basic functionality for controlling clocks, resets, and configuration pins in the CoreTile. For more information, see *3.8.4 Dual cluster system configuration block parameters* on page 3-34.

### A single external Virtual GIC

This is shared between the Cortex-A15 and Cortex-A7 clusters. For more information, see the *Virtual GIC Specification*.

Figure 1-1 Model architecture

### Related references

3.8.4 Dual cluster system configuration block parameters on page 3-34.

# Chapter 2

# Getting Started with the Cortex-A15 Cortex-A7 CCI-400 FVP

This chapter describes how to use the model. It also contains information regarding license key requirements and installation.

It contains the following sections:

- 2.1 Supported operating systems for the Cortex-A15 Cortex-A7 CCI-400 FVP on page 2-14.

- 2.2 Licenses for Cortex-A15 Cortex-A7 CCI-400 on page 2-15.

- 2.3 Installing the Cortex-A15 Cortex-A7 CCI-400 on page 2-16.

- 2.4 Running models from the command line on page 2-17.

- 2.5 Running models using Model Debugger on page 2-19.

- 2.6 Configuring the model on page 2-20.

### 2.1 Supported operating systems for the Cortex-A15 Cortex-A7 CCI-400 FVP

The Cortex-A15 Cortex-A7 CCI-400 FVP needs certain software.

**Red Hat Enterprise Linux 6.4** on 64-bit architectures. **Ubuntu 12.04 LTS** on 64-bit architectures.

Microsoft Windows 7 with Service Pack 1 on 64-bit architectures, with runtime support for Visual

Studio.

### 2.2 Licenses for Cortex-A15 Cortex-A7 CCI-400

The platform model requires FlexLm license keys to run.

The license feature names are as follows:

- SG ARM Cortex-A15 CT.

- SG\_ARM\_Cortex-A7\_CT.

- SG v7SystemIP CT.

- FM\_Simulator.

In addition, the Model Debugger requires a license key with the feature name MaxView\_Debugger.

### 2.3 Installing the Cortex-A15 Cortex-A7 CCI-400

This section describes how to install the Cortex-A15 Cortex-A7 CCI-400.

ARM provides the model as an installer package.

### **Prerequisites**

On Microsoft Windows 7, you must install runtime support for Visual Studio applications beforehand. These libraries are available free of charge from Microsoft:

http://www.microsoft.com/en-gb/download/details.aspx?id=40784

Alternatively, visit http://www.microsoft.com and search for "Visual 20xx runtime".

### **Procedure**

1. Start the installer program for the required host platform, setup.exe or setup.bin, and follow the instructions on the screen.

### 2.4 Running models from the command line

The pre-built models are supplied as *Integrated SIMulator* (ISIM) binaries.

You can execute these binaries:

- Directly from the command line.

- Indirectly using Model Debugger.

### **Options**

To run the model from the command line, type the name of the ISIM binary, for example:

The FVP\_VE\_Cortex-A15×1-A7×1 file corresponds to the ISIM binary for a Cortex-A15×1 Cortex-A7×1 CCI-400 dual cluster platform model.

The FVP\_VE\_Cortex-A15×4-A7×4 file corresponds to the ISIM binary for a Cortex-A15×4 Cortex-A7×4 CCI-400 dual cluster platform model.

The following table shows the arguments and options that you can specify on the command line.

Table 2-1 Command line options

| Short | Long option                         | Description                                                                                                                                                 |

|-------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -a    | application target=filename         | Loads the application file <i>filename</i> into processor <i>target</i> . For example: coretile.cluster0.cpu0=brot_ve.axf                                   |

| -     | data<br>target=file@[space:]address | Loads raw data from <i>file</i> at the specified <i>address</i> in the specified <i>target</i> Optionally, you can also specify a memory <i>space</i> .     |

| -     | dump<br>target=file@[space:]address | Dumps raw data into <i>file</i> from the specified <i>address</i> in the specified <i>target</i> . Optionally, you can also specify a memory <i>space</i> . |

| -b    | break target=address                | Sets a break-point at address for target.                                                                                                                   |

| -s    | start target=address                | Sets initial PC to application start address.                                                                                                               |

| -C    | parameter parameter                 | Sets a single parameter of the model. Parameters are specified as a path that names the instance and the parameter name using dot separators.               |

|       |                                     | For example: foo.bar.inst.parameter=1000                                                                                                                    |

|       |                                     | If it is necessary to set multiple parameters at the same time, use the config-file option instead.                                                         |

| -     | timelimit <i>n</i>                  | Number of seconds to run, excluding startup and shutdown. The default is unlimited.                                                                         |

| -     | cpulimit n                          | Number of host processor seconds to run, kernel and user, excluding startup and shutdown. The default is unlimited.                                         |

| -     | cyclelimit n                        | Number of cycles to run. This is ignored if -S is specified. The default is unlimited.                                                                      |

| -     | list-instances                      | Lists target instances.                                                                                                                                     |

| -1    | list-params                         | Lists target instances and their parameters.                                                                                                                |

### Table 2-1 Command line options (continued)

| -  |                       |                                                                                       |

|----|-----------------------|---------------------------------------------------------------------------------------|

|    | list-memory           | Lists memory information.                                                             |

| -f | config-file filename  | Loads model configuration parameters from file filename.                              |

| -0 | output filename       | Redirects parameter, memory, and instance lists to the output file filename.          |

| -t | cadi-trace            | Enables diagnostic output of CADI calls and call-backs.                               |

| -L | cadi-log              | Log all CADI calls into an XML logfile.                                               |

| -S | cadi-server           | Starts the CADI server and enables debuggers to connect to targets in the simulation. |

| -  | stat                  | Prints run statistics on exit.                                                        |

| •  | trace-plugin filename | Loads trace plugin filename.                                                          |

| -h | help                  | Shows command line help message and exits.                                            |

| -P | prefix                | Prefixes semi-hosting output with target instance name.                               |

| -R | run                   | Runs simulation immediately after load even with CADI server.                         |

| -V | verbose               | Specifies more verbosity about the current status.                                    |

| -v | version               | Prints version and copyright information.                                             |

| -q | quiet                 | Suppresses all informational output.                                                  |

| -  | print-port-number     | Prints the port number on which the CADI server is listening.                         |

| -k | keep-console          | Keeps the console window open after completion. Microsoft Windows only.               |

### 2.5 Running models using Model Debugger

Describes how to use the Model Debugger application to debug an application running on the model.

You can start the models directly using Model Debugger from the command line, for example:

```

modeldebugger --debug-isim bin/FVP_VE_Cortex-A15x1-A7x1 \

--application coretile.cluster0.cpu0=examples/brot_ve.axf

```

Alternatively, you can start the model using the CADI server by using the --cadi-server command line argument that 2.4 Running models from the command line on page 2-17 describes. In this case, you can start Model Debugger separately and connect it to the model using CADI by selecting:

File > Connect to Model > < select model from list > > Connect.

### **Related information**

Model Debugger for Fast Models User Guide.

### 2.6 Configuring the model

Describes how to configure Versatile Express (VE) Fixed Virtual Platforms (FVPs).

3.5 Model parameters on page 3-27 describes the valid user settings for the VE FVP parameters and their effects.

When you start the model from the command line, you can configure it using either:

- The --parameter command line argument.

- A configuration file and the --config-file command line argument.

You can configure a model started from the command line by including a reference to an optional plain text configuration file.

Each line of the configuration file must contain:

- The name of the component instance.

- The parameter to modify.

- Its value.

You must use the following format:

instance.parameter=value

The instance can be a hierarchical path, with each level separated by a dot "." character. You can include comment lines in your configuration file. These lines begin with a # character. You can set Boolean values using either true or false, or 1 or 0.

You can generate a valid configuration file with all parameters set to default values with the --list-params option by directing the output into the new configuration file.

Example 2-1 Sample configuration file including syntax examples

```

# Disable semihosting using true/false syntax

coretile.cluster0.cpu0.semihosting-enable=false

#

# Enable VFP at reset using 1/0 syntax

coretile.cluster0.cpu0.vfp-enable_at_reset=1

#

# Set the baud rate for UART 0

motherboard.pl011_uart0.baud_rate=0x4800

```

## Chapter 3

# **Programmers Reference**

Read this for a description of the functionality that the model supports, including the memory map and configuration parameters.

This chapter also describes:

- · Registers.

- · Debug behaviors.

- Expected performance.

- Known limitations.

- Functionality that is not supported.

### It contains the following sections:

- 3.1 Fixed Virtual Platforms for VE platform functionality on page 3-23.

- 3.2 Fixed Virtual Platform VE Cortex-A15 Cortex-A7 CCI-400 memory map and interrupts on page 3-24.

- 3.3 CS2 peripheral memory map on page 3-25.

- 3.4 CS3 peripheral memory map on page 3-26.

- 3.5 Model parameters on page 3-27.

- 3.6 Motherboard peripheral parameters on page 3-28.

- 3.7 Motherboard virtual component parameters on page 3-31.

- 3.8 CoreTile parameters on page 3-33.

- 3.9 Memory map differences between the VE hardware and the system model on page 3-37.

- 3.10 Memory aliasing differences between the VE hardware and the system model on page 3-38.

- 3.11 Features not present in the model on page 3-39.

- 3.12 Features partially implemented in the model on page 3-40.

- 3.13 Restrictions on the processor models on page 3-41.

- 3.14 Timing considerations on page 3-42.

- 3.15 Bus consistency messages on page 3-43.

- 3.16 Multiple entries in the cache with the same security world on page 3-44.

- 3.17 Mismatched attributes on page 3-45.

- 3.18 Cache Coherent Interconnect snoop and DVM enables on page 3-47.

- 3.19 Snoop or DVM messages received while in reset on page 3-48.

- 3.20 Invalidation of dirty lines on page 3-49.

- 3.21 Dual Cluster System Configuration Block on page 3-50.

- 3.22 Reset architecture on page 3-67.

- 3.23 Interrupt Generation Trickbox on page 3-68.

### 3.1 Fixed Virtual Platforms for VE platform functionality

The Fixed Virtual Platforms for the VE platform provide functionality for the following components:

VE motherboard model with:

- VE System Register block.

- Two Dual Timer modules, SP804.

- Watchdog module, SP805.

- System Controller, SP810.

- Four UARTs, PrimeCell PL011.

- Color LCD Controller, PrimeCell PL111 CLCD.

- Real-Time Clock, PrimeCell PL031 RTC.

- Two PS/2 keyboard and mouse interfaces, PrimeCell PL050 KMI.

- Multimedia Card Interface, PrimeCell PL180 MCI.

- Advanced Audio CODEC Interface, PrimeCell PL041 AACI.

- 10/100 Non-PCI Ethernet Controller, SMSC 91C111.

- Two 64MB areas of user NOR Flash.

- 8MB of local video SRAM.

The VE motherboard model also includes the following virtual components:

- PS/2 mouse and keyboard models connected to the PL050 KMIs.

- Visualization for CLCD display with keyboard and mouse support.

- Generic Multi-Media Card (MMC) connected to the PL180 MCI.

- Four telnet terminals, one attached to each UART.

- Flash loaders for both banks of flash.

- Audio out connected to the PL041 AACI.

- Ethernet crossover cable and host-bridge connected to the SMSC 91C111.

- Virtual File System 2 (VFS2) for host file system access.

### VE daughterboard model with the following:

- *VE Daughterboard Configuration and Control block* (VEDCC).

- VE Interrupt mapper.

- 64Kb System RAM.

- 4GB DRAM.

### ARM Cortex-A15 Cortex-A7 CoreTile models with the following:

- ARM Cortex-A15 core cluster.

- ARM Cortex-A7 core cluster.

- Shared Virtual Generic Interrupt Controller, v7 GIC-400.

- Dual Cluster System Configuration Block.

- CCI-400 Cache Coherent Interconnect.

# 3.2 Fixed Virtual Platform VE Cortex-A15 Cortex-A7 CCI-400 memory map and interrupts

The following table shows the global memory map for the platform model. This map is based on the Versatile Express RS1 memory map with the RS2 extensions.

Table 3-1 Global memory map for the platform model

| Address range               | Size  | Modeled | Description                                                                                                                                                                                            |

|-----------------------------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00_00000000-0x00_03FFFFFF | 64MB  | Yes     | NOR FLASH0, CS0.                                                                                                                                                                                       |

| 0x00_04000000-0x00_08FFFFFF | 64MB  | Yes     | Secure RAM.                                                                                                                                                                                            |

| 0x00_08000000-0x00_0BFFFFFF | 64MB  | Yes     | NOR FLASH0 alias, CS0.                                                                                                                                                                                 |

| 0x00_0C000000-0x00_0FFFFFF  | 64MB  | Yes     | NOR FLASH1, CS4.                                                                                                                                                                                       |

| 0x00_10000000-0x00_0001FFFF | -     | -       | Unused, CS5.                                                                                                                                                                                           |

| 0x00_10021000-0x00_13FFFFFF | -     | -       | Unused, CS5.                                                                                                                                                                                           |

| 0x00_14000000-0x00_17FFFFF  | -     | No      | PSRAM, CS1.                                                                                                                                                                                            |

| 0x00_18000000-0x00_1BFFFFFF | 64MB  | Yes     | Peripherals, CS2. See 3.3 CS2 peripheral memory map on page 3-25.                                                                                                                                      |

| 0x00_1C000000-0x00_1FFFFFF  | 64MB  | Yes     | Peripherals, CS3. See <i>3.4 CS3 peripheral memory map</i> on page 3-26.                                                                                                                               |

| 0x00_20000000-0x00_2BFFFFFF | -     | No      | CoreSight and peripherals.                                                                                                                                                                             |

| 0x00_2C000000-0x00_2C000FFF | -     | -       | Unused, CPU PERIPHBASE.                                                                                                                                                                                |

| 0x00_2C001000-0x00_2C007FFF | 128MB | Yes     | Shared v7 GIC-400.                                                                                                                                                                                     |

| 0x00_2C008000-0x00_2C08FFFF | -     | -       | Unused.                                                                                                                                                                                                |

| 0x00_2C090000-0x00_2C09FFFF | 64MB  | Yes     | CCI-400 PMU.                                                                                                                                                                                           |

| 0x00_2C0A0000-0x00_2CFFFFF  | -     | -       | Unused.                                                                                                                                                                                                |

| 0x00_2D000000-0x00_2DFFFFF  | -     | No      | Graphics space.                                                                                                                                                                                        |

| 0x00_2E000000-0x00_2E00FFFF | 64MB  | Yes     | System SRAM.                                                                                                                                                                                           |

| 0x00_2E010000-0x07_FFFFFFF  | -     | No      | Ext AXI.                                                                                                                                                                                               |

| 0x00_60000000-0x00_60000FFF | 4KB   | Yes     | Dual Cluster System Configuration Block.                                                                                                                                                               |

| 0x00_80000000-0x00_FFFFFFF  | 2GB   | Yes     | 4GB DRAM, in 32-bit address space. The model contains 4GB of DRAM The DRAM memory address space is aliased across the three different regions, and where the mapped address space is greater than 4GB. |

| 0x01_00000000-0x07_FFFFFFF  | -     | -       | Unused.                                                                                                                                                                                                |

| 0x08_00000000-0x08_FFFFFFF  | 4GB   | Yes     | 4GB DRAM, in 36-bit address space. The model contains 4GB of DRAM The DRAM memory address space is aliased across the three different regions, and where the mapped address space is greater than 4GB. |

| 0x09_00000000-0x7F_FFFFFFF  |       | -       | Unused.                                                                                                                                                                                                |

| 0x80_00000000-0xFF_FFFFFFF  | 512GB | Yes     | 4GB DRAM, in 40-bit address space. The model contains 4GB of DRAM The DRAM memory address space is aliased across the three different regions, and where the mapped address space is greater than 4GB. |

### 3.3 CS2 peripheral memory map

The following table shows the memory map for peripherals in the CS2 region.

Table 3-2 CS2 peripheral memory map

| Address range               | Size | Int | Modeled | Description           |

|-----------------------------|------|-----|---------|-----------------------|

| 0x00_18000000-0x00_19FFFFF  | 32MB | -   | Yes     | 8MB VRAM              |

| 0x00_1A000000-0x00_1AFFFFF  | 16MB | 47  | Yes     | Ethernet, SMSC 91C111 |

| 0x00_1B000000-0x00_1BFFFFFF | 16MB | -   | No      | USB                   |

### 3.4 CS3 peripheral memory map

The following table shows the memory map for peripherals in the CS3 region.

Table 3-3 CS3 peripheral memory map

| Address range                  | Size  | Int    | Modeled | Description                    |

|--------------------------------|-------|--------|---------|--------------------------------|

| 0x00_1C000000-0x 0x00_1C00FFFF | 64KB  | -      | No      | Local DAP ROM                  |

| 0x00_1C010000-0x 0x00_1C01FFFF | 64KB  | -      | Yes     | VE System Registers            |

| 0x00_1C020000-0x 0x00_1C02FFFF | 64KB  | -      | Yes     | System Controller, SP810       |

| 0x00_1C030000-0x00_1C03FFFF    | 64KB  | -      | No      | TwoWire serial interface, PCIe |

| 0x00_1C040000-0x00_1C04FFFF    | 64KB  | 43     | Partial | AACI, PL041                    |

| 0x00_1C050000-0x00_1C05FFFF    | 64KB  | 41, 42 | Partial | MCI, PL180                     |

| 0x00_1C060000-0x00_1C06FFFF    | 64KB  | 44     | Yes     | KMI, keyboard, PL050           |

| 0x00_1C070000-0x00_1C07FFFF    | 64KB  | 45     | Yes     | KMI, mouse, PL050              |

| 0x00_1C080000-0x00_1C08FFFF    | 64KB  | -      | -       | Reserved                       |

| 0x00_1C090000-0x00_1C09FFFF    | 64KB  | 37     | Yes     | UARTO, PL011                   |

| 0x00_1C0A0000-0x00_1C0AFFFF    | 64KB  | 38     | Yes     | UART1, PL011                   |

| 0x00_1C0B0000-0x00_1C0BFFFF    | 64KB  | 39     | Yes     | UART2, PL011                   |

| 0x00_1C0C0000-0x00_1C0CFFFF    | 64KB  | 40     | Yes     | UART3, PL011                   |

| 0x00_1C0D0000-0x00_1C0EFFFF    | 64KB  | 73     | Yes     | VFS2                           |

| 0x00_1C0D0000-0x00_1C0EFFFF    | 64KB  | -      | -       | Reserved                       |

| 0x00_1C0F0000-0x00_1C0FFFFF    | 64KB  | 32     | Yes     | Watchdog, SP805                |

| 0x00_1C100000-0x00_1C10FFFF    | 64KB  | -      | -       | Reserved                       |

| 0x00_1C110000-0x00_1C11FFFF    | 64KB  | 34     | Yes     | Timer-0, SP804                 |

| 0x00_1C120000-0x00_1C12FFFF    | 64KB  | 35     | Yes     | Timer-1, SP804                 |

| 0x00_1C130000-0x00_1C15FFFF    | 192KB | -      | -       | Reserved                       |

| 0x00_1C160000-0x00_1C16FFFF    | 64KB  | -      | No      | TwoWire serial interface, DVI  |

| 0x00_1C170000-0x00_1C17FFFF    | 64KB  | 36     | Yes     | Real-time Clock, PL031         |

| 0x00_1C180000-0x00_1C19FFFF    | 128KB | -      | -       | Reserved                       |

| 0x00_1C1A0000-0x00_1C1AFFFF    | 64KB  | -      | No      | CF card                        |

| 0x00_1C1B0000-0x00_1C1EFFFF    | 256KB | -      | -       | Reserved                       |

| 0x00_1C1F0000-0x00_1C1FFFFF    | 64KB  | 46     | Yes     | Color LCD Controller, PL111    |

| 0x00_1C200000-0x00_1FFFFFF     | 62MB  | -      | -       | Reserved                       |

|                                |       |        |         |                                |

### 3.5 Model parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.parameter=value

Table 3-4 FVP\_VE\_Cortex-A15x1-A7x1 parameters

| Parameter | Туре | Allowed values | Default value | Description                              |

|-----------|------|----------------|---------------|------------------------------------------|

| proc_id0  | int  | -              | 0xC000000     | Processor ID at CoreTile Express Site 1. |

| proc_id1  | int  | -              | 0xFF000000    | Processor ID at CoreTile Express Site 2. |

Table 3-5 FVP\_VE\_Cortex-A15x4-A7x4 parameters

| Parameter | Type | Allowed values | Default value | Description                              |

|-----------|------|----------------|---------------|------------------------------------------|

| proc_id0  | int  | -              | 0x14000000    | Processor ID at CoreTile Express Site 1. |

| proc_id1  | int  | -              | 0xFF000000    | Processor ID at CoreTile Express Site 2. |

### 3.6 Motherboard peripheral parameters

This section describes the motherboard peripheral parameters.

This section contains the following subsections:

- 3.6.1 Color LCD controller parameters on page 3-28.

- 3.6.2 Ethernet parameters on page 3-28.

- 3.6.3 MAC address parameter on page 3-28.

- 3.6.4 System controller parameters on page 3-29.

- 3.6.5 VE System Register block parameters on page 3-29.

- 3.6.6 UART parameters on page 3-29.

- 3.6.7 Watchdog parameter on page 3-30.

### 3.6.1 Color LCD controller parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.pl111 clcd.parameter=value

Table 3-6 Color LCD controller parameters

| Parameter                     | Туре | Allowed values | Default value | Description                                                                                                              |

|-------------------------------|------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| <pre>pixel_double_limit</pre> | int  | -              | 12C           | The threshold, in horizontal pixels, below which pixels sent to the frame-buffer are doubled in size in both dimensions. |

### 3.6.2 Ethernet parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

$\verb|motherboard.smsc_91c111.| parameter = value|$

**Table 3-7 Ethernet parameters**

| Parameter   | Type   | Allowed values                               | Default value     | Description                                                                                                |

|-------------|--------|----------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|

| enabled     | bool   | true, false                                  | false             | Host interface connection enabled.                                                                         |

| mac_address | string | See 3.6.3 MAC address parameter on page 3-28 | 00:02:f7:ef:60:30 | Host and model MAC address.                                                                                |

| promiscuous | bool   | true, false                                  | true              | Places the host into promiscuous mode, for example, when sharing the Ethernet controller with the host OS. |

### 3.6.3 MAC address parameter

There are options available for the mac address parameter.

- If a MAC address is not specified, when the simulator is run, it takes the default MAC address and changes its bottom two bytes from 00:02 to the bottom two bytes of the MAC address of one of the adaptors on the host PC. This provides some degree of MAC address uniqueness when running models on multiple hosts on a local network.

- 2. If you specify the MAC address as auto, this generates a completely random local MAC address each time the simulator is run. The address has bit 1 set and bit 0 clear in the first byte to indicate a locally-administered unicast MAC address.

DHCP servers allocate IP addresses, but because they sometimes do this based on the MAC address provided to them, then using random MAC addresses might interact unfavorably with some DHCP servers.

### 3.6.4 System controller parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.sp810\_sysctrl.parameter=value

Table 3-8 System controller configuration parameters

| Parameter | Туре | Allowed values | Default value | Description                                   |

|-----------|------|----------------|---------------|-----------------------------------------------|

| sysid     | int  | -              | 0x00000000    | Value for the system identification register. |

| use_s8    | bool | true, false    | false         | Select whether switch S8 is enabled.          |

### 3.6.5 VE System Register block parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.ve\_sysregs.parameter=value

Table 3-9 VE system register block parameters

| Parameter           | Туре | Allowed values | Default value | Description             |

|---------------------|------|----------------|---------------|-------------------------|

| user_switches_value | int  | -              | 0x00          | User switch.            |

| tilePresent         | bool | true, false    | true          | CoreTile fitted status. |

### 3.6.6 UART parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.pl011\_uartx.parameter=value

x is the UART identifier 0, 1, 2, or 3.

Table 3-10 UART parameters

| Parameter               | Type   | Allowed values | Default value | Description                                                         |

|-------------------------|--------|----------------|---------------|---------------------------------------------------------------------|

| baud_rate               | int    | -              | 0x9600        | Baud rate.                                                          |

| clock_rate              | int    | -              | 0xE10000      | Clock rate for PL011.                                               |

| in_file                 | string | -              | ""            | Input file.                                                         |

| out_file                | string | -              | ""            | Output file, use "-" to send all output to stdout.                  |

| in_file_escape_sequence | string | -              | ##            | Input file escape sequence string.                                  |

| shutdown_on_eot         | bool   | true, false    | false         | Shutdown simulation when an EOT, ASCII 4, character is transmitted. |

### Table 3-10 UART parameters (continued)

| Parameter         | Туре | Allowed values | Default value | Description                                                            |

|-------------------|------|----------------|---------------|------------------------------------------------------------------------|

| unbuffered_output | bool | true, false    | false         | Unbuffered output.                                                     |

| untimed_fifos     | bool | true, false    | false         | Ignore the clock rate and transmit or receive serial data immediately. |

| uart_enable       | bool | true, false    | false         | Enable the UART when the system starts.                                |

### 3.6.7 Watchdog parameter

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.sp805\_wdog.parameter=value

Table 3-11 Watchdog parameter

| Parameter | Type | Allowed values | Default value | Description    |

|-----------|------|----------------|---------------|----------------|

| simhalt   | bool | true, false    | false         | Halt on reset. |

### 3.7 Motherboard virtual component parameters

This section describes the motherboard virtual component parameters.

This section contains the following subsections:

- 3.7.1 FLASH loader parameters on page 3-31.

- 3.7.2 Host bridge parameter on page 3-31.

- 3.7.3 Multimedia card parameters on page 3-31.

- 3.7.4 Terminal parameters on page 3-32.

- *3.7.5 VFS2 parameter* on page 3-32.

- *3.7.6 Visualization parameters* on page 3-32.

### 3.7.1 FLASH loader parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.flashloaderx.parameter=value

x is the FLASH identifier 0 or 1.

Table 3-12 FLASH loader parameters

| Parameter  | Type   | Allowed values  | Default value | Description                                                                                                  |

|------------|--------|-----------------|---------------|--------------------------------------------------------------------------------------------------------------|

| fname      | string | Valid file name | -             | Path to the host file that initializes FLASH contents when the model starts. You can gzip compress the file. |

| fnameWrite | string | Valid file name | -             | Path to the host file used to save FLASH contents when the model exits.                                      |

### 3.7.2 Host bridge parameter

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.hostbridge.parameter=value

Table 3-13 Host bridge parameter

| Parameter     | Туре   | Allowed values | Default value | Description                |

|---------------|--------|----------------|---------------|----------------------------|

| interfaceName | string | Valid string   | ARM0          | Host Interface identifier. |

### 3.7.3 Multimedia card parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.mmc.parameter=value

Table 3-14 Multimedia card parameters

| Parameter  | Туре   | Allowed values       | Default value | Description                                    |

|------------|--------|----------------------|---------------|------------------------------------------------|

| p_mmc_file | string | Valid filename       | mmc.dat       | File used for the MMC component backing store. |

| p_prodName | string | Six character string | ARMmmc        | Card ID product name.                          |

| p_prodRev  | int    | -                    | 0x1           | Card ID product revision.                      |

| p_manid    | int    | -                    | 0x2           | Card ID manufacturer ID.                       |

Table 3-14 Multimedia card parameters (continued)

| Parameter | Type | Allowed values | Default value | Description         |

|-----------|------|----------------|---------------|---------------------|

| p_OEMid   | int  | -              | 0x0000        | Card ID OEM ID.     |

| p_sernum  | int  | -              | 0xCA4D0001    | Card serial number. |

### 3.7.4 Terminal parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.terminal x.parameter=value

x is the terminal identifier 0, 1, 2, or 3.

**Table 3-15 Terminal parameters**

| Parameter    | Туре   | Allowed values    | Default value | Description                                                                                                                                          |

|--------------|--------|-------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| mode         | string | telnet, raw       | telnet        | Terminal initialization mode.                                                                                                                        |

| start_telnet | bool   | true, false       | true          | Enables the terminal when the system starts.                                                                                                         |

| start_port   | int    | Valid port number | 5000          | Port used for the terminal when the system starts. If the specified port is not free, the port value is incremented by 1 until a free port is found. |

### 3.7.5 VFS2 parameter

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.vfs2.parameter=value

Table 3-16 VFS2 parameter

| Parameter | Туре   | Allowed values | Default value | Description                                              |

|-----------|--------|----------------|---------------|----------------------------------------------------------|

| mount     | string | Valid path     | -             | Path to host folder to make accessible inside the model. |

### 3.7.6 Visualization parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

motherboard.vis.parameter=value

Table 3-17 Visualization parameters

| Parameter             | Type | Allowed values | Default value      | Description                                                         |

|-----------------------|------|----------------|--------------------|---------------------------------------------------------------------|

| trap_key              | int  | 0x00-0xFF      | 0x4A, left Alt key | Trap key that works with the left Ctrl to toggle the mouse display. |

| rate_limit-enable     | bool | true, false    | true               | Rate limit simulation.                                              |

| disable_visualization | bool | true, false    | false              | Disables visualization.                                             |

### 3.8 CoreTile parameters

This section describes the CoreTile parameters.

This section contains the following subsections:

- 3.8.1 Cluster parameters on page 3-33.

- 3.8.2 Core parameters on page 3-33.

- 3.8.3 GIC-400 parameters on page 3-34.

- 3.8.4 Dual cluster system configuration block parameters on page 3-34.

- *3.8.5 CCI-400 parameters* on page 3-35.

### 3.8.1 Cluster parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

coretile.clusterx.parameter=value

x 0 for the Cortex-A15 cluster, 1 for the Cortex-A7 cluster.

Table 3-18 Cluster parameters

| Parameter                      | Type     | Allowed values             | Default value                          | e Description                                      |                                    |  |

|--------------------------------|----------|----------------------------|----------------------------------------|----------------------------------------------------|------------------------------------|--|

| CFGDISABLE bool true, false fa |          | false                      | Disables some access to DIC registers. |                                                    |                                    |  |

| CLUSTER_ID                     | int 0-15 |                            | 0                                      | Cluster ID value.                                  |                                    |  |

| device-accurate-tlb            | bool     | true, false                | false                                  | Sets whether device-accurate number of TI modeled. |                                    |  |

| dic-spi_count                  | int      | 0-224, in increments of 32 | 64                                     | Number of share implemented.                       | ed peripheral interrupts           |  |

| IMINLN                         | bool     | true, false                | true                                   | Instruction cache not cluster 1.                   | e minimum line size for cluster 0, |  |

|                                |          |                            |                                        | false                                              | 32 bytes.                          |  |

|                                |          |                            |                                        | true                                               | 64 bytes.                          |  |

| l1_dcache-<br>state_modelled   | bool     | true,false                 | false                                  | Includes Level 1                                   | data cache state model.            |  |

| l1_icache-<br>state_modelled   | bool     | true, false                | false                                  | Includes Level 1                                   | instruction cache state model.     |  |

| 12_cache-size                  | int      | 512KB, 1MB, 2MB,<br>4MB    | 0x80000                                | Sets Level 2 cac                                   | he size in bytes integer.          |  |

| l2_cache-<br>state_modelled    | bool     | true,false                 | false                                  | Includes Level 2 cache state model.                |                                    |  |

### 3.8.2 Core parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

coretile.clusterx.cpuy.parameter=value

- x 0 for the Cortex-A15 cluster, 1 for the Cortex-A7 cluster.

- y the core index, in the range 0-3.

Table 3-19 Core parameters

| Parameter                   | Type | Allowed values        | Default value | Description                                                                              |

|-----------------------------|------|-----------------------|---------------|------------------------------------------------------------------------------------------|

| CFGEND                      | bool | true, false           | false         | Initializes to BE8 endianness.                                                           |

| CFGNMFI                     | bool | true, false           | false         | Enables non-maskable fast interrupts on startup.                                         |

| CP15SDISABLE                | bool | true, false           | false         | Initializes to disable access to some CP15 registers.                                    |

| TEINIT                      | bool | true, false           | false         | Thumb exception enable. The default has exceptions including reset handled in ARM state. |

| VINITHI                     | bool | true, false           | false         | Initializes with high vectors enabled.                                                   |

| SMPnAMP                     | bool | true, false           | false         | Sets whether the processor is part of a coherent domain.                                 |

| POWERCTLI                   | int  | 0x0-0x3               | 0x0           | Default power control state for core.                                                    |

| semihosting-enable          | bool | true, false           | true          | Enables semi-hosting SVC traps.                                                          |

| semihosting-ARM_SVC         | int  | 0x000000-0xFFFFFF     | 0x123456      | ARM SVC number for semi-hosting.                                                         |

| semihosting-Thumb-SVC       | int  | 0x00-0xFF             | 0xAB          | Thumb SVC number for semi-hosting integer.                                               |

| semihosting-heap_base       | int  | 0x00000000- 0xFFFFFFF | 0x0           | Virtual address of heap base.                                                            |

| semihosting-heap_limit      | int  | 0x00000000-0xFFFFFFF  | 0x0           | Virtual address of heap limit integer.                                                   |

| semihosting-stack_base      | int  | 0x00000000-0xFFFFFFF  | 0x0           | Virtual address of stack base.                                                           |

| semihosting-<br>stack_limit | int  | 0x00000000-0xFFFFFFF  | 0x0           | Virtual address of stack limit.                                                          |

| vfp-enable_at_reset         | bool | true, false           | false         | Enables coprocessor access and VFP at reset.                                             |

| vfp-preset                  | bool | true, false           | true          | Sets whether the model has VFP support.                                                  |

| ase-present                 | bool | true, false           | true          | Sets whether the model has NEON support.                                                 |

### 3.8.3 GIC-400 parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is:

coretile.v7\_vgic.parameter=value

Table 3-20 GIC-400 parameters

| Parameter           | Type | Allowed values | Default value | Description                                                                  |

|---------------------|------|----------------|---------------|------------------------------------------------------------------------------|

| enabled             | bool | true, false    | true          | Enables the component. If disabled, then no register writes have any effect. |

| enable_log_warnings | bool | true, false    | false         | Enables warning messages.                                                    |

| enable_log_errors   | bool | true, false    | false         | Enables error messages.                                                      |

| enable_log_fatal    | bool | true, false    | false         | Enables fatal messages.                                                      |

### 3.8.4 Dual cluster system configuration block parameters

You set these instantiation-time parameters when starting the model.

The syntax to use in a configuration file or on the command line is: coretile.dualclustersytemconfigurationblock.parameter=value

Table 3-21 Dual cluster system configuration block parameters

| Parameter                            | Type | Allowed values    | Default value | Description                                                                                |  |  |

|--------------------------------------|------|-------------------|---------------|--------------------------------------------------------------------------------------------|--|--|

| CFG_ACTIVECLUSTER                    | int  | 0x1-0x3, bit mask | 0x1           | Select the cluster that comes out of reset at power on:                                    |  |  |

|                                      |      |                   |               | <b>Bit[0]</b> For the Cortex-A15.                                                          |  |  |

|                                      |      |                   |               | <b>bit[1]</b> For the Cortex-A7.                                                           |  |  |

| Cluster0IdOnPOReset                  |      | 0x0-0xF           | 0x0           | Cortex-A15 Cluster ID on power-on reset.                                                   |  |  |

| Cluster1IdOnPOReset                  | int  | 0x0-0xF           | 0x1           | Cortex-A7 Cluster ID on power-on reset.                                                    |  |  |

| DCS_LED                              | bool | 0x00-0xFF         | 0x00          | Initial value of the DCS_LED register that represents the state of the daughterboard LEDs. |  |  |

| ResetValueOfDaughterUserSwitches     | int  | 0x00-0xFF         | 0x00          | The state of the daughterboard user switches at reset.                                     |  |  |

| INTGEN_INTS                          | int  | 0-3               | 3             | Number of custom IRQs that the interrupt generator controls is (INTGEN_INTS × 32) + 32.    |  |  |

| DCS_ID                               | int  | 0x0-0xFFFFFFF     | 0x41120000    | The value returned by the DCS_ID register.                                                 |  |  |

| FlipVGICWiringForCluster0AndCluster1 | bool | true, false       | false         | true If this is true, then core 0 of cluster 1 becomes core interface 0 on the GIC-400.    |  |  |

|                                      |      |                   |               | false If this is false, then core 0 of cluster 0 becomes core interface 0 on the GIC-400.  |  |  |

### 3.8.5 CCI-400 parameters

You set these instantiation-time parameters when starting the model. The syntax to use in a configuration file or on the command line is:

coretile.cci400.parameter=value

Table 3-22 CCI-400 configuration parameters

| Parameter          | Туре | Allowed values    | Default<br>value | Description                                                                                                             |

|--------------------|------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| broadcastcachemain | int  | 0x0-0x7, bit mask | 0x0              | For each downstream port, a bit determines whether broadcast cache maintenance operations are forwarded down that port. |

| barrierterminate   | int  | 0x0-0x7, bit mask | 0x7              | For each downstream port, determines whether barriers are terminated at that port.                                      |

### Table 3-22 CCI-400 configuration parameters (continued)

| Parameter           | Туре | Allowed values                | Default<br>value | Poscription  For each downstream port, determines whether all transactions are forced to non-bufferable.  The CCI-400 normally starts up with snooping disabled. This parameter enables snooping when the model starts without it being necessary to program it. This parameter applies to simulation reset, not at signal reset. |  |

|---------------------|------|-------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bufferableoverride  | int  | 0x0-0x7, bit mask             |                  |                                                                                                                                                                                                                                                                                                                                   |  |

| force_on_from_start | bool | true, false                   | false            |                                                                                                                                                                                                                                                                                                                                   |  |

| log_enabled         | int  | O Logging off.                | 1                | Enables log messages from the CCI-400 register file.                                                                                                                                                                                                                                                                              |  |

|                     |      | 1 Log only access violations. |                  |                                                                                                                                                                                                                                                                                                                                   |  |

|                     |      | 2 Also log writes.            |                  |                                                                                                                                                                                                                                                                                                                                   |  |

|                     |      | 3 Also log reads.             |                  |                                                                                                                                                                                                                                                                                                                                   |  |

# 3.9 Memory map differences between the VE hardware and the system model

The model is based on the memory map of the hardware VE platform. However, it is not intended to be an accurate representation of a specific VE hardware revision.

The memory map in the supplied model is sufficiently complete and accurate to boot the same operating system images as for the VE hardware. In the memory map, memory regions that are not explicitly occupied by a peripheral, or by memory, are unmapped. This includes:

- Regions otherwise occupied by a peripheral that is not implemented.

- Areas that are specified as being reserved.

If a host processor accesses these regions, the model issues a warning.

The model implements address space aliasing of the DRAM. This means that the same physical memory locations are visible at different addresses.

The lower 2GB of the DRAM is accessible at 0x00\_80000000.

The full 4GB of DRAM is accessible at 0x08\_00000000, and again at 0x80\_00000000.

The aliasing of DRAM then repeats from 0x81\_00000000 up to 0xFF\_FFFFFFF.

# 3.11 Features not present in the model

Some features in the hardware version of the Versatile Express motherboard are not implemented in the system models.

The following features are not implemented in the system models:

- Two-wire serial bus interfaces.

- USB interfaces.

- PCI Express interfaces.

- Compact Flash.

- DVI interfaces.

- Debug and test interfaces.

- Dynamic Memory Controller (DMC).

- Static Memory Controller (SMC).

- CoreSight.

# 3.12 Features partially implemented in the model

Partial implementation means that some of the components are present, but their functionality has not been fully modeled.

If you use these features, they might not work as you expect. Check the model release notes for the latest information.

#### Sound

The VE FVPs implement the PL041 AACI PrimeCell and the audio CODEC in the same way as in the VE hardware, but with a limited number of sample rates.

# 3.13 Restrictions on the processor models

Separate documentation contains detailed information regarding the features that are not fully implemented in the processor models that are included with the VE *Fixed Virtual Platforms* (FVPs). See the Fast Models Reference Manual.

The following general restrictions apply to the FVP implementations of ARM processors:

- The simulator does not model cycle timing. In aggregate, all instructions execute in one core master clock cycle, with the exception of Wait For Interrupt.

- Write buffers are not modeled.

- Most aspects of *Translation Lookaside Buffer* (TLB) behavior are implemented in the models.

Architecture v7 models use the TLB memory attribute settings when you enable stateful cache.

- No MicroTLB is implemented.

- A single memory access port is implemented. The port combines accesses for:

- Instruction

- Data.

- DMA.

- Peripherals.

Configuration of the peripheral port memory map register is ignored.

- All memory accesses are atomic and are performed in programmers view order. All transactions on the PVBus are a maximum of 32 bits wide. Unaligned accesses are always performed as byte transfers

- Some instruction sequences are executed atomically, ahead of the component master clock, so that

system time advances during their execution. This can sometimes have an effect in sequential access

of device registers where devices expect time to progress between each access.

- Interrupts are not taken at every instruction boundary.

- The semihosting-debug configuration parameter is ignored.

- · Integration and test registers are not implemented.

- Not all CP14 debug registers are implemented.

- You must use an external debugger to debug an FVP.

- The model supports the following breakpoint types:

- Single address unconditional instruction breakpoints.

- Single address unconditional data breakpoints.

- Unconditional instruction address range breakpoints.

- Pseudo-registers in the debugger support processor exception breakpoints. Setting an exception register to a non-zero value stops execution on entry to the associated exception vector.

- Performance counters are not implemented.

# 3.14 Timing considerations

The Fixed Virtual Platforms provide environments that enable you to run software applications in a functionally-accurate simulation.

However, because of the relative balance of fast simulation speed compared to timing accuracy, situations exist where the models might behave unexpectedly. When code interacts with real world devices such as timers and keyboards, data arrives in the modeled device in real world, or wall clock, time, but simulation time can be running much faster than the wall clock.